QSBASE5¶

This guide will help new users to quickly setup our QSBASE5 Linux Development Kit.

Detailed information about the QS solder-in module itself is available on our website.

Unboxing¶

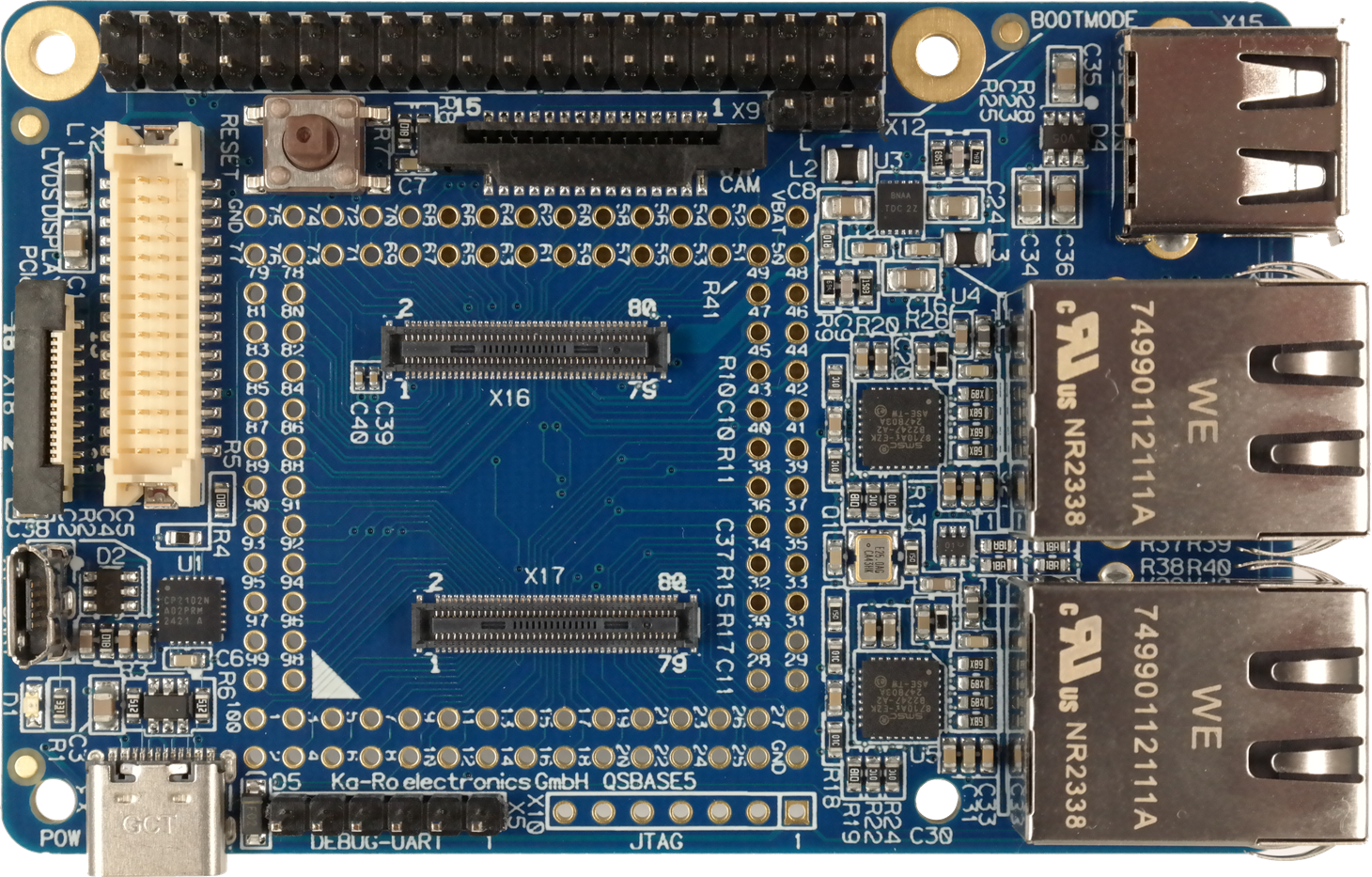

When opening the package of the Development Kit you should find the following components inside:

|

|

|

Wiring¶

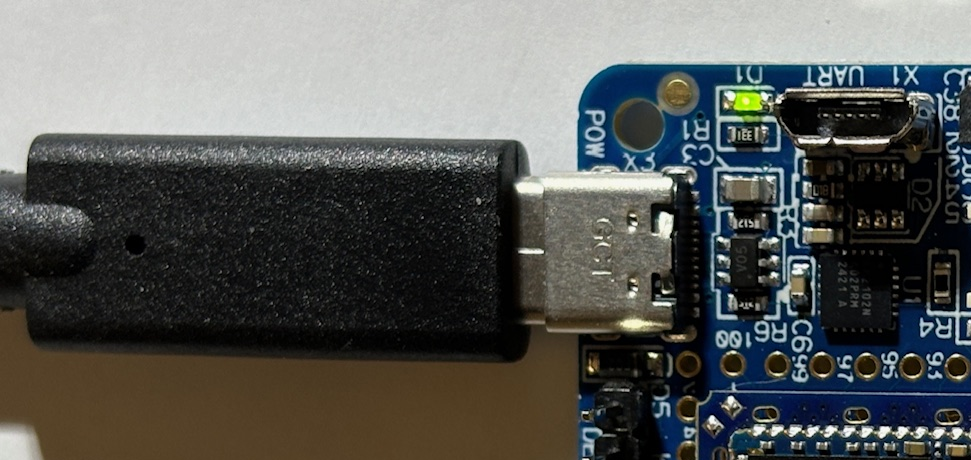

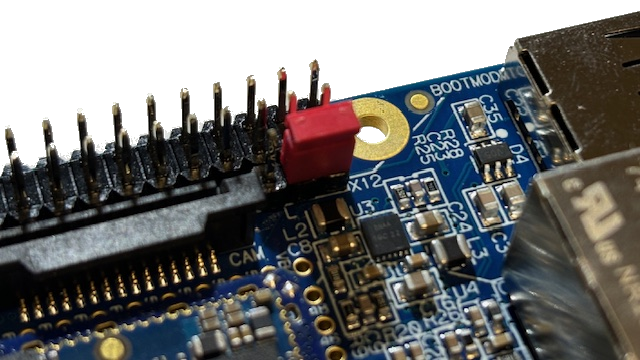

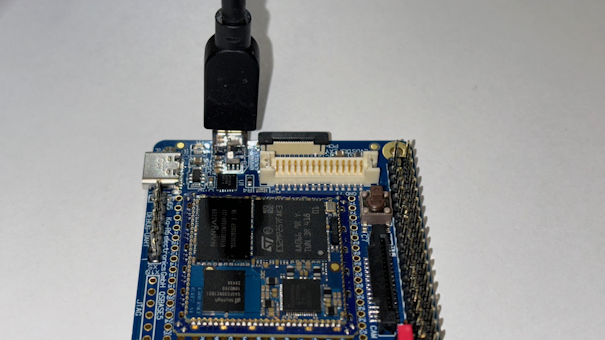

Connect the QSBASE5 board as shown in the image below.

|

|

|

This USB connection is used for both power supply and programming. |

This USB connection is used for the terminal |

|

|

|

|

The board may require more current than a standard USB 2.0 port can deliver. |

USB-UART driver¶

Download and Install USB to UART Bridge Virtual COM Port (VCP) drivers

Booting¶

After connecting the power supply your board will boot.

INIT: version 3.04 booting

Initializing /var... Done.

Starting udev

fsck from util-linux 2.38.1

e2fsck 1.47.0 (5-Feb-2023)

/dev/mmcblk0p3: clean, 3850/32768 files, 104708/131072 blocks

fsck from util-linux 2.38.1

e2fsck 1.47.0 (5-Feb-2023)

bootfs: clean, 28/16384 files, 23703/65536 blocks

ALSA: Restoring mixer settings...

INIT: Entering runlevel: 2

Configuring network interfaces... dhcpcd-9.4.1 starting

eth0: waiting for carrier

NOTICE: Early console setup

NOTICE: CPU: STM32MP257FAK Rev.Y

NOTICE: Model: Ka-Ro electronics GmbH QSMP-2550 module

NOTICE: PCA9450A chip ID = 0x11

NOTICE: BL2: v2.8-stm32mp2-r2.1(release):v2.8-stm32mp-r2.1-dirty(c536182a)

NOTICE: BL2: Built : 12:54:23, Dec 17 2024

NOTICE: BL2: Booting BL31

NOTICE: Early console setup

NOTICE: BL31: v2.8-stm32mp2-r2.1(release):v2.8-stm32mp-r2.1-dirty(c536182a)

NOTICE: BL31: Built : 12:54:23, Dec 17 2024

I/TC: Early console on UART#4

I/TC:

I/TC: Embedded DTB found

I/TC: OP-TEE version: 3.19.0-stm32mp-r2.1-dev (gcc version 12.3.0 (GCC)) #1 Tue Dec 17 12:58:14 UTC 2024 aarch64

I/TC: WARNING: This OP-TEE configuration might be insecure!

I/TC: WARNING: Please check https://optee.readthedocs.io/en/latest/architecture/porting_guidelines.html

I/TC: Primary CPU initializing

I/TC: WARNING: All debug access are allowed

I/TC: RISAF 0x420e0000: No configuration in DT, use default

I/TC: PMIC PCA9450A 0x11

E/TC:0 0 pwr_set_low_volt:249 vddio2: failed to set VRSEL; make sure the HSLV_VDDIO2 fuse is correctly configured

I/TC: Platform stm32mp2: flavor PLATFORM_FLAVOR - DT stm32mp255f-qsmp-2550.dts

I/TC: OP-TEE ST profile: secure_and_system_services

I/TC: DTB enables console (non-secure)

[ 0.000000] SCP-firmware 3.19.0-stm32mp-r2.1-dev

[ 0.000000]

[ 0.000000] [FWK] Module initialization complete!

I/TC: Primary CPU switching to normal world boot

U-Boot 2022.10-stm32mp-r2-karo+g712876e9bd (Dec 17 2024 - 13:45:08 +0000)

CPU: STM32MP257FAK Rev.Y

Model: Ka-Ro electronics GmbH QSMP-2550 solder-in module on QSBASE5 baseboard

Board: QSMP-2550 (karo,stm32mp255f-qsmp-2550)

DRAM: 1 GiB

Core: 315 devices, 25 uclasses, devicetree: board

MMC: STM32 SD/MMC: 1, STM32 SD/MMC: 0

Loading Environment from MMC... *** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

MAC addr from fuse: 00:0c:c6:0f:6d:cc

Loading DTB from mmc 0:2 'stm32mp255f-qsmp-2550.dtb'

Loading FDT overlay for 'qsmp-csi' from mmc 0:2 'stm32mp25-qsmp-csi.dtb'

Loading FDT overlay for 'qsmp-eth1-lan8710' from mmc 0:2 'stm32mp25-qsmp-eth1-lan8710.dtb'

Loading FDT overlay for 'qsmp-eth2-lan8710' from mmc 0:2 'stm32mp25-qsmp-eth2-lan8710.dtb'

Loading FDT overlay for 'qsmp-fdcan1' from mmc 0:2 'stm32mp25-qsmp-fdcan1.dtb'

Loading FDT overlay for 'qsmp-fdcan2' from mmc 0:2 'stm32mp25-qsmp-fdcan2.dtb'

Loading FDT overlay for 'qsmp-qsbase5' from mmc 0:2 'stm32mp25-qsmp-qsbase5.dtb'

Loading FDT overlay for 'qsmp-lvds-panel' from mmc 0:2 'stm32mp25-qsmp-lvds-panel.dtb'

Loading FDT overlay for 'qsmp-pcie' from mmc 0:2 'stm32mp25-qsmp-pcie.dtb'

Loading FDT overlay for 'qsmp-spidev1' from mmc 0:2 'stm32mp25-qsmp-spidev1.dtb'

Loading FDT overlay for 'qsmp-spidev2' from mmc 0:2 'stm32mp25-qsmp-spidev2.dtb'

Loading FDT overlay for 'karo-panel-tm101jvhg32' from mmc 0:2 'stm32mp25-karo-panel-tm101jvhg32.dtb'

Net: eth0: eth1@482c0000, eth1: eth2@482d0000

Hit any key to stop autoboot: 1 0

15501320 bytes read in 338 ms (43.7 MiB/s)

## Flattened Device Tree blob at 8a000000

Booting using the fdt blob at 0x8a000000

Loading Device Tree to 000000008bfe3000, end 000000008bffffff ... OK

serial-number: 003D0

NOTICE: Early console setup

NOTICE: CPU: STM32MP257FAK Rev.Y

NOTICE: Model: Ka-Ro electronics GmbH QSMP-2550 module

NOTICE: PCA9450A chip ID = 0x11

NOTICE: BL2: v2.8-stm32mp2-r2.1(release):v2.8-stm32mp-r2.1-dirty(c536182a)

NOTICE: BL2: Built : 12:54:23, Dec 17 2024

NOTICE: BL2: Booting BL31

NOTICE: Early console setup

NOTICE: BL31: v2.8-stm32mp2-r2.1(release):v2.8-stm32mp-r2.1-dirty(c536182a)

NOTICE: BL31: Built : 12:54:23, Dec 17 2024

I/TC: Early console on UART#4

I/TC:

I/TC: Embedded DTB found

I/TC: OP-TEE version: 3.19.0-stm32mp-r2.1-dev (gcc version 12.3.0 (GCC)) #1 Tue Dec 17 12:58:14 UTC 2024 aarch64

I/TC: WARNING: This OP-TEE configuration might be insecure!

I/TC: WARNING: Please check https://optee.readthedocs.io/en/latest/architecture/porting_guidelines.html

I/TC: Primary CPU initializing

I/TC: WARNING: All debug access are allowed

I/TC: RISAF 0x420e0000: No configuration in DT, use default

I/TC: PMIC PCA9450A 0x11

E/TC:0 0 pwr_set_low_volt:249 vddio2: failed to set VRSEL; make sure the HSLV_VDDIO2 fuse is correctly configured

I/TC: Platform stm32mp2: flavor PLATFORM_FLAVOR - DT stm32mp255f-qsmp-2550.dts

I/TC: OP-TEE ST profile: secure_and_system_services

I/TC: DTB enables console (non-secure)

[ 0.000000] SCP-firmware 3.19.0-stm32mp-r2.1-dev

[ 0.000000]

[ 0.000000] [FWK] Module initialization complete!

I/TC: Primary CPU switching to normal world boot

U-Boot 2022.10-stm32mp-r2-karo+g712876e9bd (Dec 17 2024 - 13:45:08 +0000)

CPU: STM32MP257FAK Rev.Y

Model: Ka-Ro electronics GmbH QSMP-2550 solder-in module on QSBASE5 baseboard

Board: QSMP-2550 (karo,stm32mp255f-qsmp-2550)

DRAM: 1 GiB

Core: 315 devices, 25 uclasses, devicetree: board

MMC: STM32 SD/MMC: 1, STM32 SD/MMC: 0

Loading Environment from MMC... *** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

MAC addr from fuse: 00:0c:c6:0f:6d:cc

Loading DTB from mmc 0:2 'stm32mp255f-qsmp-2550.dtb'

Loading FDT overlay for 'qsmp-csi' from mmc 0:2 'stm32mp25-qsmp-csi.dtb'

Loading FDT overlay for 'qsmp-eth1-lan8710' from mmc 0:2 'stm32mp25-qsmp-eth1-lan8710.dtb'

Loading FDT overlay for 'qsmp-eth2-lan8710' from mmc 0:2 'stm32mp25-qsmp-eth2-lan8710.dtb'

Loading FDT overlay for 'qsmp-fdcan1' from mmc 0:2 'stm32mp25-qsmp-fdcan1.dtb'

Loading FDT overlay for 'qsmp-fdcan2' from mmc 0:2 'stm32mp25-qsmp-fdcan2.dtb'

Loading FDT overlay for 'qsmp-qsbase5' from mmc 0:2 'stm32mp25-qsmp-qsbase5.dtb'

Loading FDT overlay for 'qsmp-lvds-panel' from mmc 0:2 'stm32mp25-qsmp-lvds-panel.dtb'

Loading FDT overlay for 'qsmp-pcie' from mmc 0:2 'stm32mp25-qsmp-pcie.dtb'

Loading FDT overlay for 'qsmp-spidev1' from mmc 0:2 'stm32mp25-qsmp-spidev1.dtb'

Loading FDT overlay for 'qsmp-spidev2' from mmc 0:2 'stm32mp25-qsmp-spidev2.dtb'

Loading FDT overlay for 'karo-panel-tm101jvhg32' from mmc 0:2 'stm32mp25-karo-panel-tm101jvhg32.dtb'

Net: eth0: eth1@482c0000, eth1: eth2@482d0000

Hit any key to stop autoboot: 0

QSMP U-Boot >

Your module is pre-programmed with our karo-image-minimal headless Linux.

Next Steps Usage¶

Topic |

Description |

|---|---|

Re-installing the OS |

|

Next Steps Software¶

Topic |

Description |

|---|---|

Linux Guide |

Go to: Software Documentation |

WiFi Guide |

To enable WiFi support. Go to: Software Documentation -> WiFi/BT Guide |

Camera Guide |

To enable camera support. Go to: Software Documentation -> Camera Guide |

Google Coral Edge TPU |

How to use Google Coral PCIe ML accelerator. Go to: Software Documentation -> Coral Edge TPU |

Machine Learning |

Using NPU and starting ML Demos. Go to: Software Documentation -> Machine Learning Guide |

QT5 Development |

Develop a QT5 app for your customers. Go to: Software Documentation -> QT Guide |

Electron Development |

Develop an Electron app for your customers. Go to: Software Documentation -> Electron |

Customizing the BSP |

If you want to use our Yocto Layer, or want to create your own customized Linux distribution, have a look at our Yocto Guide. Go to: Yocto Guide |

Next Steps Hardware¶

Topic |

Description |

|---|---|

QSBASE5 Pinouts |

Connector pinouts can be found in the Hardware Documentation. Go to: Hardware Documentation -> Pinouts -> QSBASE5 |

QS Developers Guide |

QS-Standard pinout, description and layout guidelines. Go to: Hardware Documentation -> QS-GUIDE |